Why?How?一文为你深度分析时钟抖动!

品慧电子讯时钟接口阈值区间附近的抖动会破坏ADC的时序。例如,抖动会导致ADC在错误的时间采样,造成对模拟输入的误采样,并且降低器件的信噪比(SNR)。降低抖动有很多不同的方法,但是,在get降低抖动的方法前我们必须找到抖动的根本原因!

时钟抖动,why?

时钟抖动的根本原因就是时钟和ADC之间的电路噪声。随机抖动由随机噪声引起,主要随机噪声源包括

● 热噪声(约翰逊或奈奎斯特噪声),由载流子的布朗运动引起。

● 散粒噪声,与流经势垒的直流电流有关,该势垒不连续平滑,由载流子的单独流动引起的电流脉冲所造成。

● 闪烁噪声,出现在直流电流流动时。该噪声由携带载流子的半导体中的陷阱引起,这些载流子在释放前通常会形成持续时间较短的直流电流。

● 爆裂噪声,也称爆米花噪声,由硅表面的污染或晶格错位造成,会随机采集或释放载流子。

ps.以上噪声我们曾将详细讲解过,有兴趣的筒子点击蓝色字体查看~

查看时钟信号噪声,how?

确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。查看时钟信号噪声通常有三种途径:时域、频域、相位域。

咳咳,敲黑板划重点,以上三种途径的具体方法如下↓↓↓

时域图

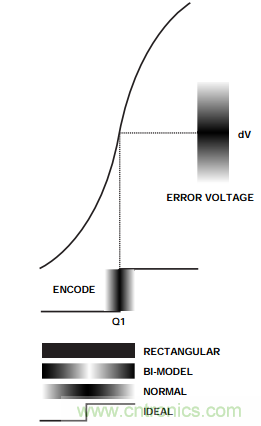

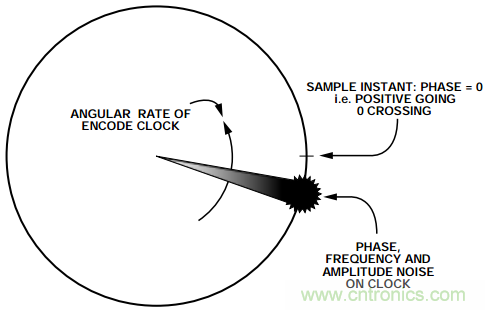

图1. 抖动的时域图

时钟抖动是编码时钟的样本(不同周期)间的变化,包括外部和内部抖动。抖动引起的满量程信噪比由以下公式得出

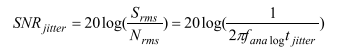

举个栗子,频率为1 Ghz,抖动为100 FS均方根值时,信噪比为64 dB。在时域中查看时,x轴方向的编码边沿变化会导致y轴误差,幅度取决于边沿的上升时间。孔径抖动会在ADC输出产生误差,如图2所示。抖动可能产生于内部的ADC、外部的采样时钟或接口电路。

图2. 孔径抖动和采样时钟抖动的影响

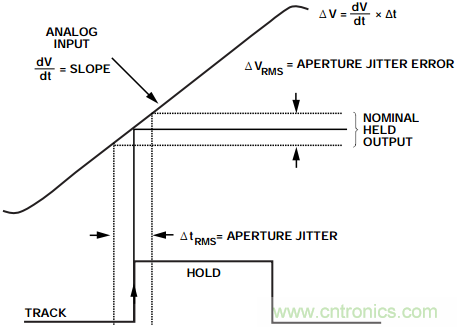

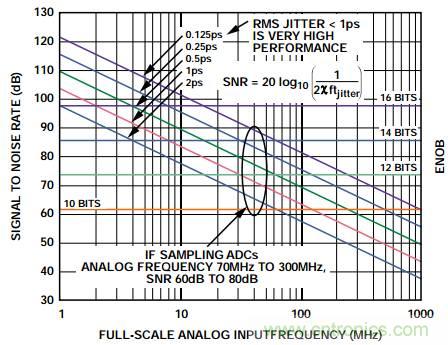

图3显示抖动对信噪比的影响。图中显示了5条线,分别代表不同的抖动值。x轴是满量程模拟输入频率,y轴是由抖动引起的信噪比,有别于ADC总信噪比。

图3. 时钟抖动随模拟信号增大而提升信噪比

由抖动引起的信噪比和有效位数(ENOB)的关系由以下公式定义:

SNR = 6.02 N + 1.76 dB

其中N =有效位数。满量程100 MHz输入时,14位有效位数要求均方根抖动不超过0.125 ps或125 fs。该公式假定ADC具有无限分辨率,其中的唯一误差是由时钟抖动产生的噪声。

图4. 由抖动产生的理论信噪比和有效位数与满量程正弦波模拟输入频率的关系

频域图

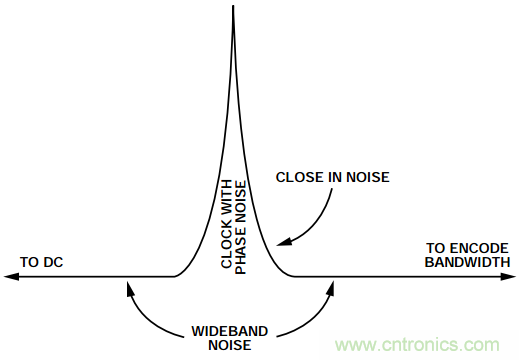

近载波噪声出现在采样时钟中心频率和等于信号带宽一半的单边带(SSB)失调之间。宽带噪声的范围从单边带失调到½时钟接收器带宽。

图5. 频域图

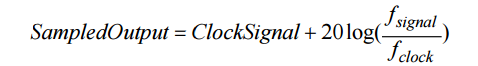

时间的乘法运算是在频域中进行卷积。因此,时钟上在频域上的任何“裙边”都会施加于数字信号。这会增加信号的EVM,降低整体性能。卷积到采样信号上的噪声量取决于模拟频率与采样频率的关系。

图6.卷积到采样信号上的噪声取决于模拟频率和采样频率的关系

相位域图

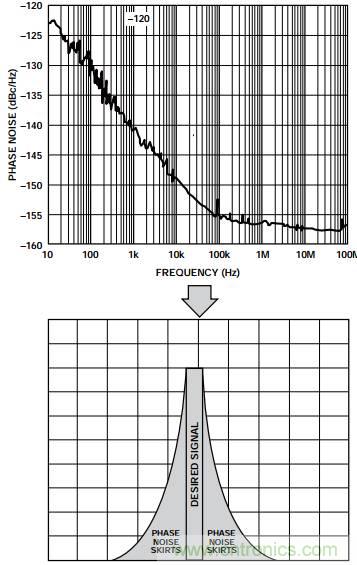

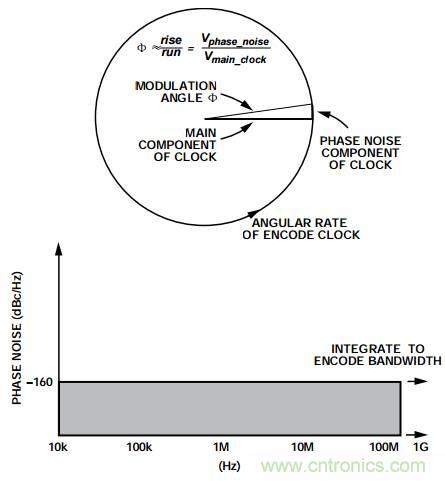

相位噪声由每个时钟周期之间的时间变化引起。最终结果是时钟信号在基波频率周围变化,这一频率范围变化会降低ADC的信噪比。

图7.抖动的相位域图

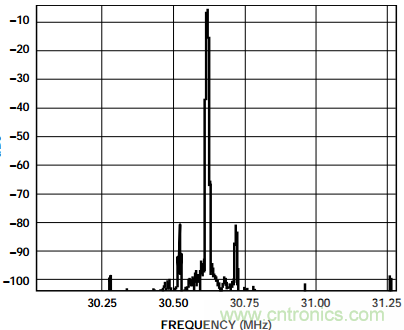

图8所示的例子中,−66 dBc的杂散增加到78 MHz时钟上,用来将ADC采样控制在30.62 MHz模拟信号。

图8. 使用噪声时钟采样时的30.62 MHz信号

杂散为−74.1 dBc,按以下公式计算:

![]()

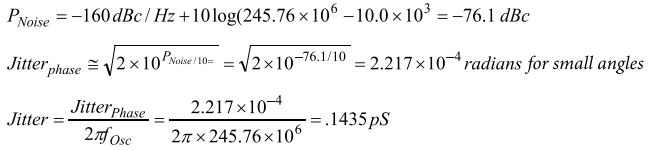

时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

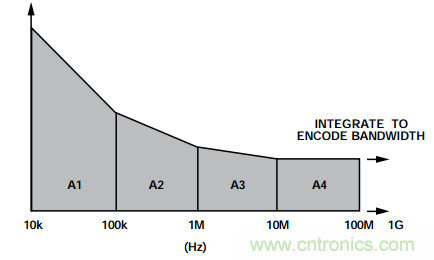

图9. 对编码带宽的近载波到时钟输出噪声进行积分计算

高度为−160 dBc,宽度为10 KHz至245.76 MHz。因此,

10×log(245.7e6 − 10e3)

= 83.9 dB,−160 + 83.9 dB

= 76.1 dBc

得出积分噪声。

载波的失调不同,噪声的斜率也不同。例如,A1区域通常为1/f噪声,而A4区域则视为宽带噪声。

图10.在频率范围内的噪声变化情况

A =面积=积分相位噪声功率(dBc)抖动可以通过对编码带宽的近载波到时钟输出的噪声进行积分计算确定。频率范围应分为较小的频带,然后相加得到总的结果:A = 10 log10 (A1 + A2 + A3 + A4)

本文转载自ADI.

推荐阅读:

简化数据中心和电信电源系统设计,就靠它了!

电阻硫化机理