硬件开发,我想和MOS管聊聊

品慧电子讯MOS 管作为半导体领域最基础的器件之一,无论是在IC 设计里,还是板级电路应用上,都十分广泛。目前尤其在大功率半导体领域,各种结构的 MOS 管更是发挥着不可替代的作用。作为一个基础器件,往往集简单与复杂与一身,简单在于它的结构,复杂在于基于应用的深入考量。

因此,作为硬件开发者,想在电路设计上进阶,搞懂 MOS 管是必不可少的一步,今天来聊聊。

一、 MOS 管的半导体结构

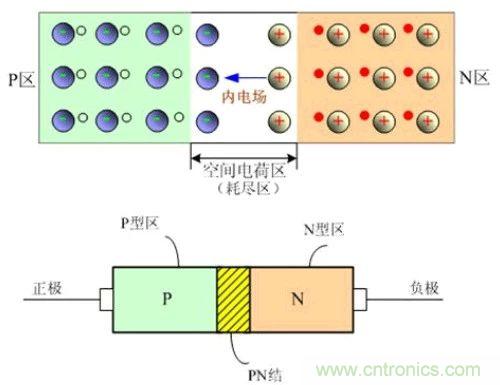

作为半导体器件,它的来源还是最原始的材料,掺杂半导体形成的 P 和 N 型物质。

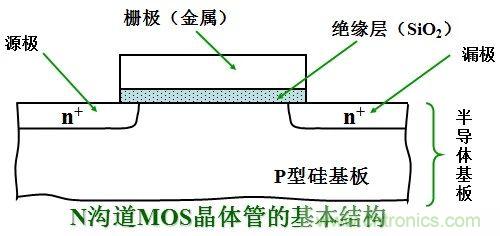

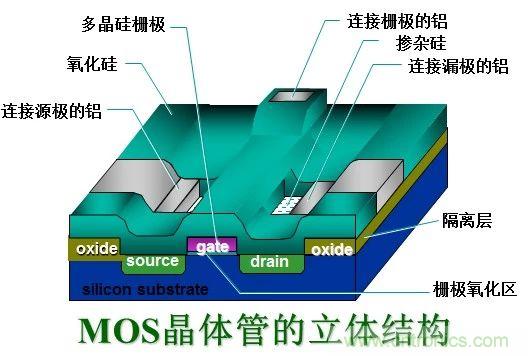

那么,在半导体工艺里,如何制造 MOS 管的?

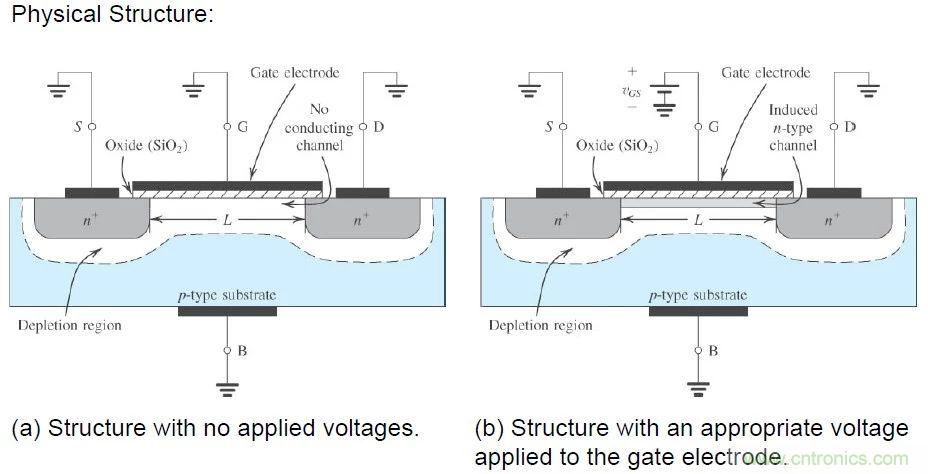

这就是一个 NMOS 的结构简图,一个看起来很简单的三端元器件。具体的制造过程就像搭建积木一样,在一定的地基(衬底)上依据设计一步步“盖”起来。

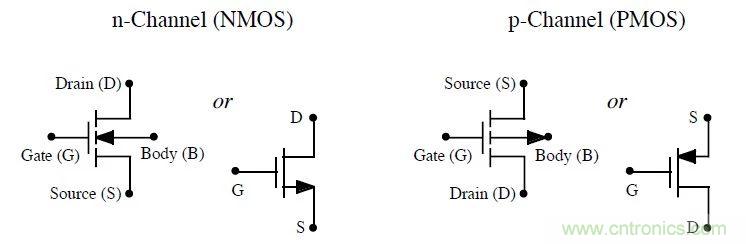

MOS 管的符号描述为:

二、 MOS 管的工作机制

以增强型 MOS 管为例,我们先简单来看下 MOS 管的工作原理。

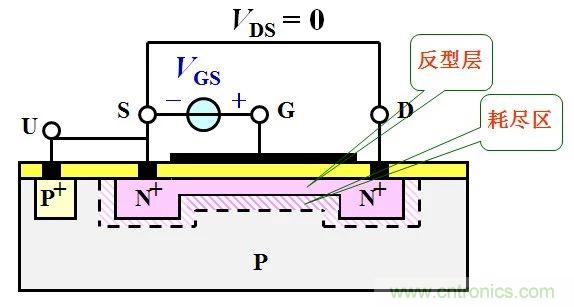

由上图结构我们可以看到 MOS 管类似三极管,也是背靠背的两个PN结!三极管的原理是在偏置的情况下注入电流到很薄的基区通过电子-空穴复合来控制CE之间的导通,MOS 管则利用电场来在栅极形成载流子沟道来沟通DS之间。

如上图,在开启电压不足时,N区和衬底P之间因为载流子的自然复合会形成一个中性的耗尽区。

给栅极提供正向电压后,P区的少子(电子)会在电场的作用下聚集到栅极氧化硅下,最后会形成一个以电子为多子的区域,叫反型层,称为反型因为是在P型衬底区形成了一个N型沟道区。这样DS之间就导通了。

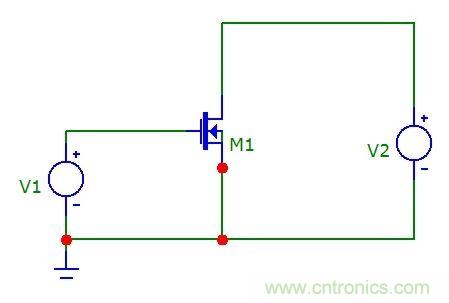

下图是一个简单的MOS管开启模拟:

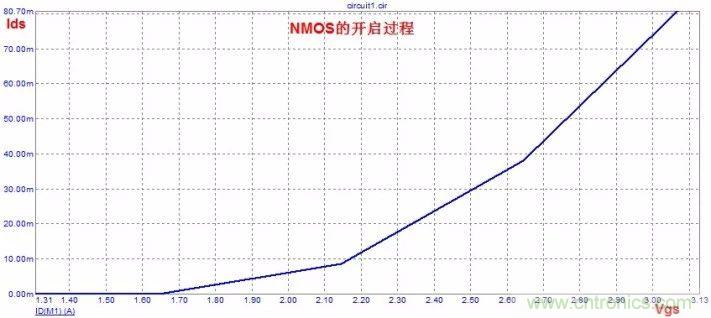

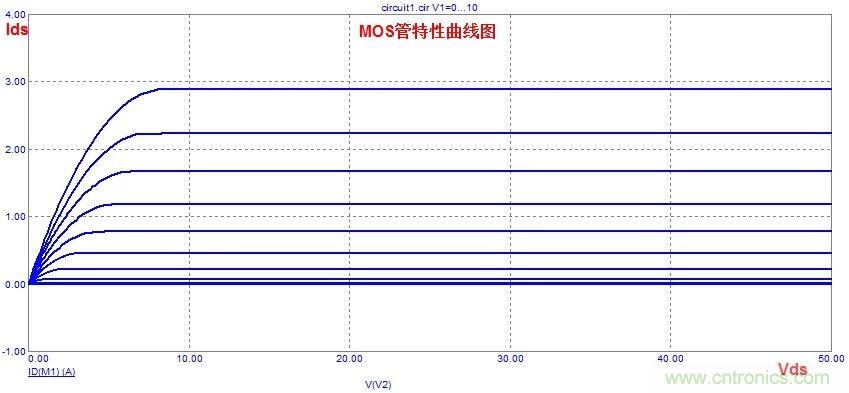

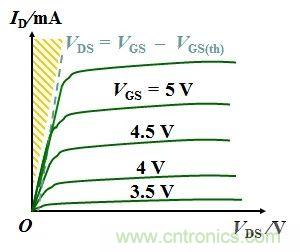

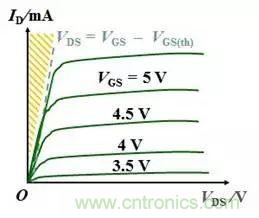

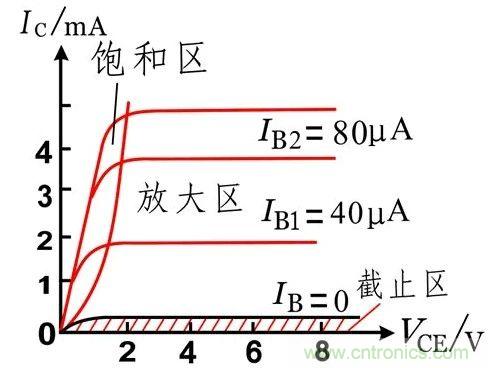

这是MOS管电流Id随Vgs变化曲线,开启电压为1.65V。下图是MOS管的IDS和VGS与VDS 之间的特性曲线图,类似三极管。

下面我们先从器件结构的角度看一下MOS管的开启全过程。

1、 Vgs 对MOS 管的开启作用

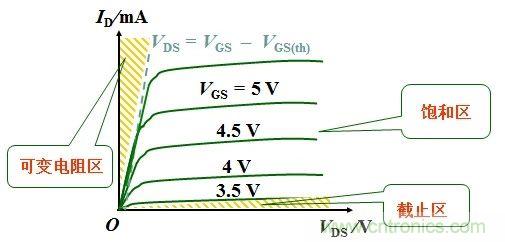

一定范围内 Vgs>Vth,Vds<Vgs-Vth,Vgs 越大,反型层越宽,电流越大。这个区域为 MOS 管的线性区(可变电阻区)。即:

Vgs 为常数时,Vds 上升,Id 近似线性上升,表现为一种电阻特性。

Vds 为常数时,Vgs 上升,Id 近似线性上升,表现出一种压控电阻的特性。

即曲线左边

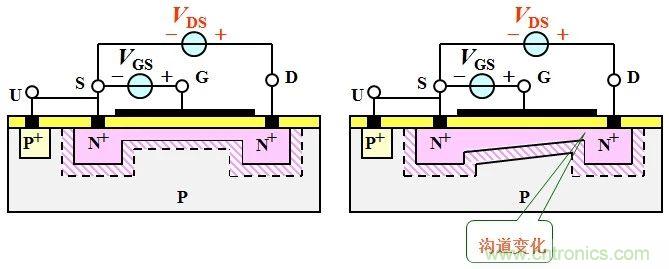

2、 Vds对MOS管沟道的控制

当Vgs>Vth,Vds<Vgs-Vth时,分析同上曲线左侧,电流Id随Vds上升而上升,为可变电阻区。

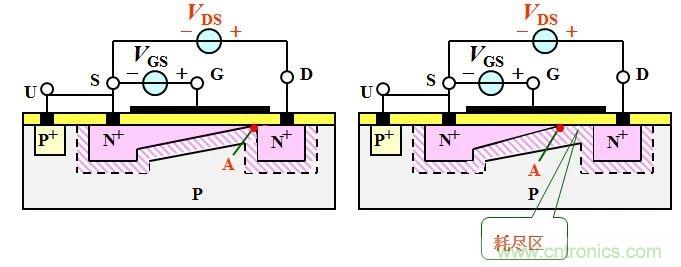

当Vds>Vgs-Vth后,我们可以看到因为DS之间的电场开始导致右侧的沟道变窄,电阻变大。所以电流Id增加开始变缓慢。当Vds增大一定程度后,右沟道被完全夹断了!

此时DS之间的电压都分布在靠近D端的夹断耗尽区,夹断区的增大即沟道宽度W减小导致的电阻增大抵消了Vds对Id的正向作用,因此导致电流Id几乎不再随Vds增加而变化。此时的D端载流子是在强电场的作用下扫过耗尽区达到S端!

这个区域为 MOS 管的恒流区,也叫饱和区,放大区。

但是因为有沟道调制效应导致沟道长度 L 有变化,所以曲线稍微上翘一点。

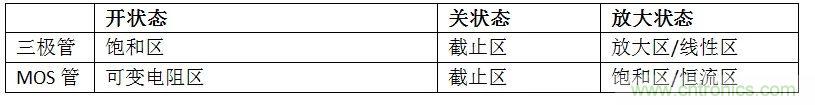

重点备注:MOS 管与三极管的工作区定义差别

三极管的饱和区:输出电流 Ic 不随输入电流 Ib 变化。

MOS 管的饱和区:输出电流 Id 不随输出电压 Vds 变化。

3、击穿

Vgs 过大会导致栅极很薄的氧化层被击穿损坏。

Vds 过大会导致D和衬底之间的反向PN结雪崩击穿,大电流直接流入衬底。

三、 MOS 管的开关过程分析

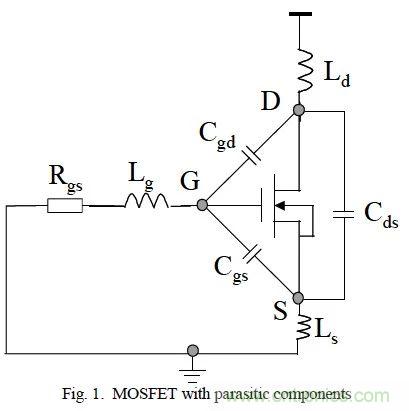

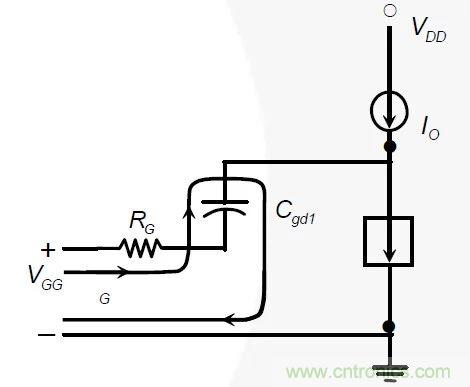

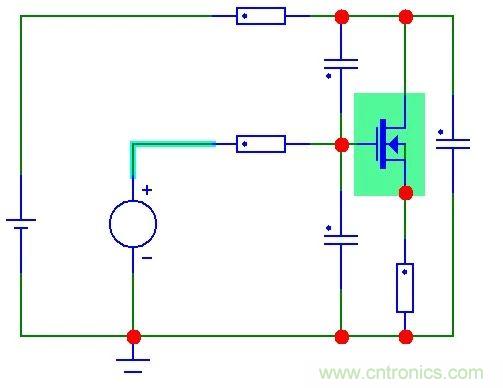

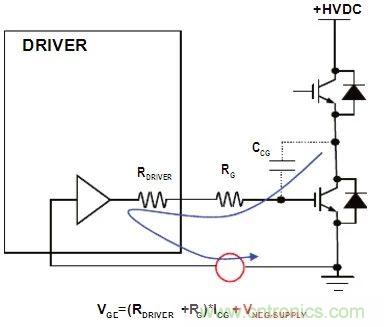

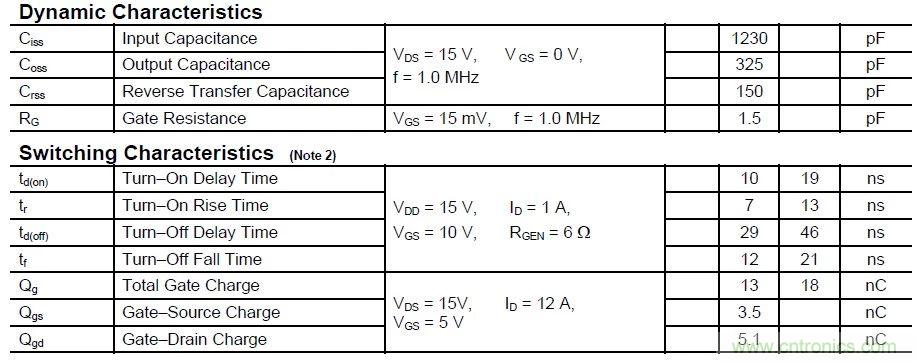

如果要进一步了解MOS管的工作原理,剖析MOS管由截止到开启的全过程,必须建立一个完整的电路结构模型,引入寄生参数,如下图。

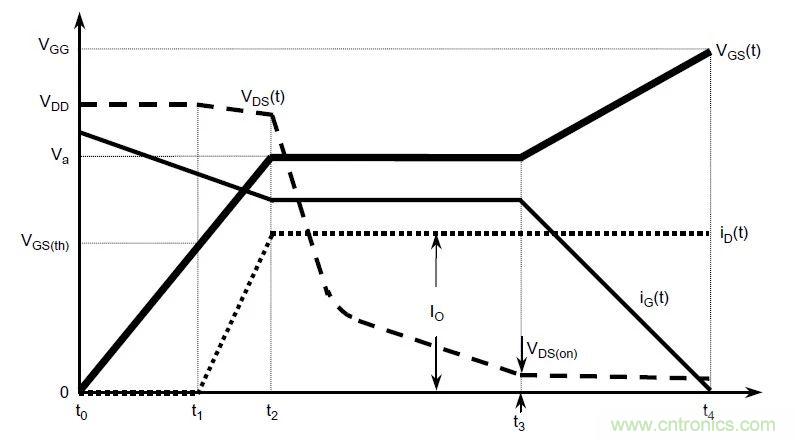

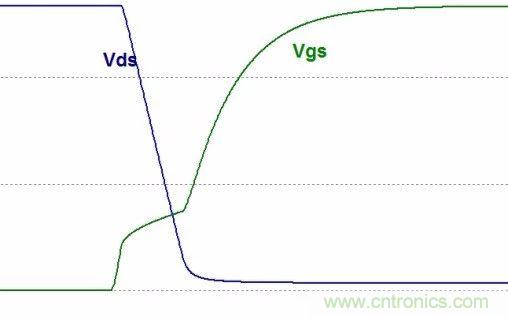

详细开启过程为:

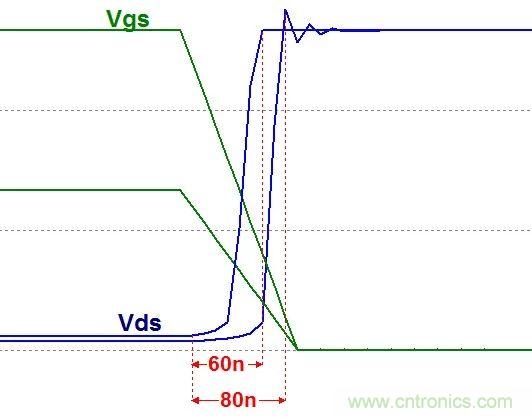

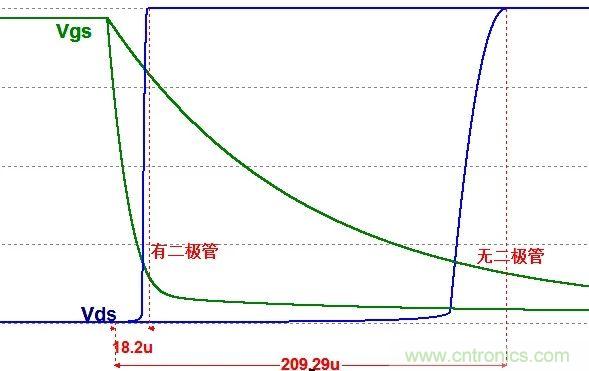

t0~t1阶段:栅极电流对Cgs和Cgd充电,Vgs上升到开启电压Vgs(th),此间,MOS没有开启,无电流通过,即MOS管的截止区。在这个阶段,显然Vd电压大于Vg,可以理解为电容 Cgd 上正下负。

t1~t2 阶段:Vgs达到Vth后,MOS管开始逐渐开启至满载电流值Io,出现电流Ids,Ids与Vgs呈线性关系,这个阶段是MOS管的可变电阻区,或者叫线性区。

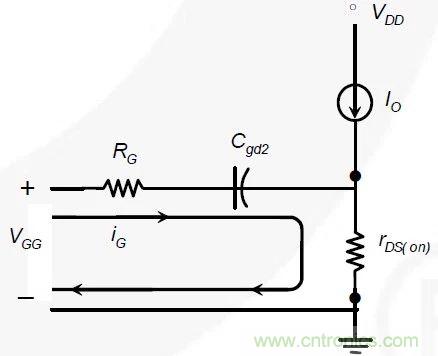

t2~t3阶段:在MOS完全开启达到电流Io后,栅极电流被完全转移到Ids中,导致Vgs保持不变,出现米勒平台。在米勒平台区域,处于MOS管的饱和区,或者叫放大区。

在这一区域内,因为米勒效应,等效输入电容变为(1+K)Cgd。

米勒效应如何产生的:

在放大区的 MOS管,米勒电容跨接在输入和输出之间,为负反馈作用。具体反馈过程为:Vgs 增大>mos开启后Vds开始下降>因为米勒电容反馈导致Vgs 也会通过Cgd放电下降。这个时候,因为有外部栅极驱动电流,所以才会保持了Vgs 不变,而Vds还在下降。

t3~t4阶段:渡过米勒平台后,即Cgd反向充电达到Vgs,Vgs继续升高至最终电压,这个电压值决定的是MOS管的开启阻抗Ron大小。

我们可以通过仿真看下具体过程:

由上面的分析可以看出米勒平台是有害的,造成开启延时,不能快速进入可变电阻区,导致损耗严重,但是这个效应又是无法避免的。

目前减小 MOS 管米勒效应的几种措施:

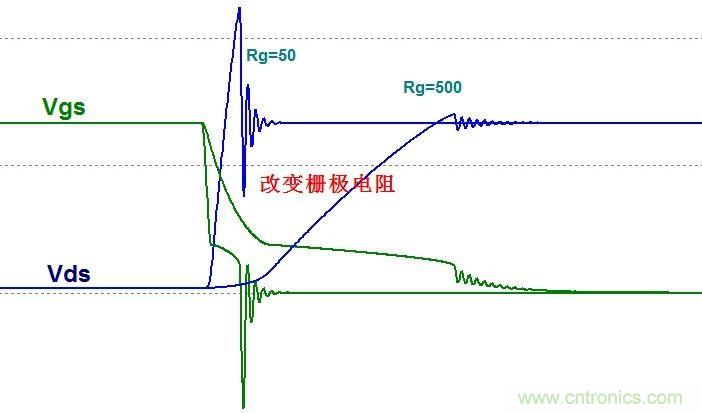

a: 提高驱动电压或者减小驱动电阻,目的是增大驱动电流,快速充电。但是可能因为寄生电感带来震荡问题。

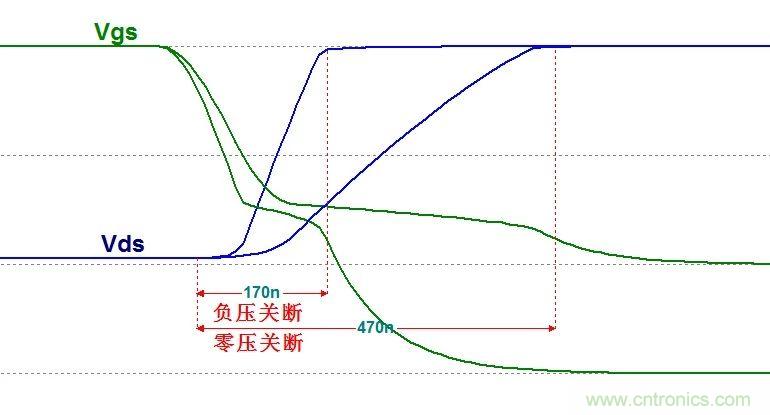

b: ZVS 零电压开关技术是可以消除米勒效应的,即在 Vds 为 0 时开启沟道,在大功率应用时较多。

c: 栅极负电压驱动,增加设计成本。

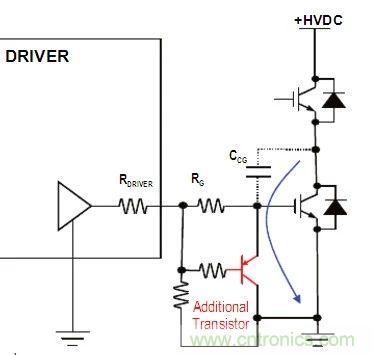

d: 有源米勒钳位。即在栅极增加三极管,关断时拉低栅极电压。

四、 MOS 管的驱动应用

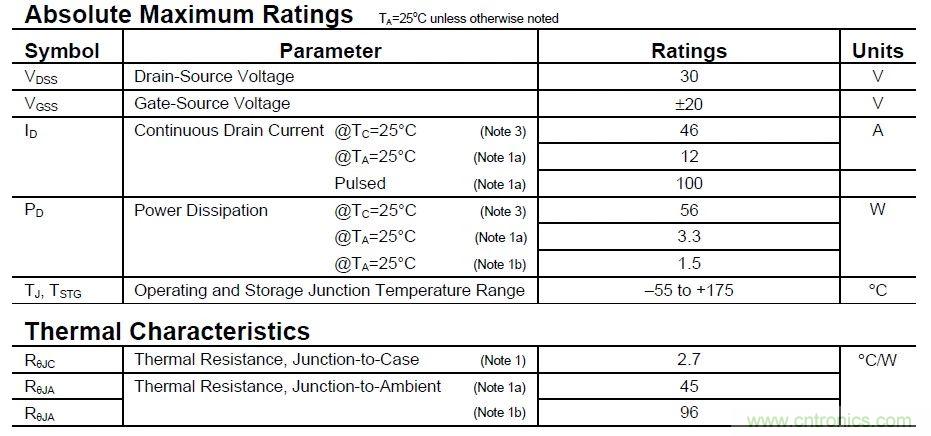

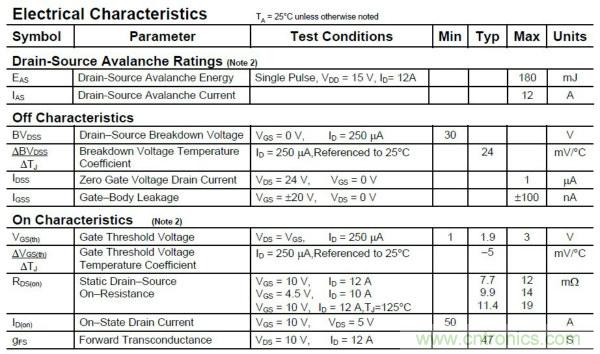

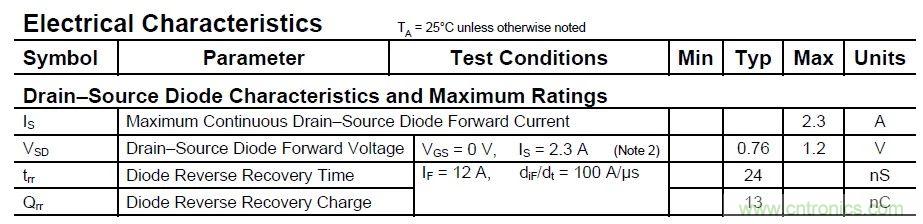

上面已经详细介绍了 MOS 管的工作机制,那么我们再来看 datasheet 这些参数就一目了然了。

极限值参数代表应用时的最高范围,功耗和散热是高功率应用时的重点。

功率应用中尤其考虑导通电阻、米勒电容等,高速应用中重点考虑寄生电容。

漏电流的参数一般影响的是大规模集成芯片的功耗。

反向恢复时间是一个重要参数,它表示 MOS 管由开启到截止的恢复时间,时间太长会极大影响速度和功耗。

体二极管:

在分立器件NMOS管中,S端一般衬底,所以导致DS之间有一个寄生二极管。

但是在集成电路内部,S端接低电位或者高电位,不一定接衬底,所以就不存在寄生二极管。

寄生二极管具有保护 MOS 管的作用,导出瞬间反向的大电流。

MOS 的驱动是应用设计的重点,接下来我们聊聊有哪些驱动方式和特点。

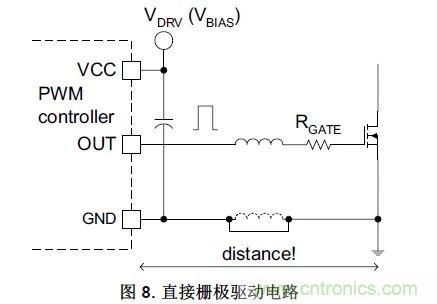

4.1 直接驱动

驱动芯片直接输出 PWM 波

特点:驱动环路距离不能太远,否则因为寄生电感降低开关速度和导致振铃。另外,一般驱动器也难以提供很大的驱动电流。

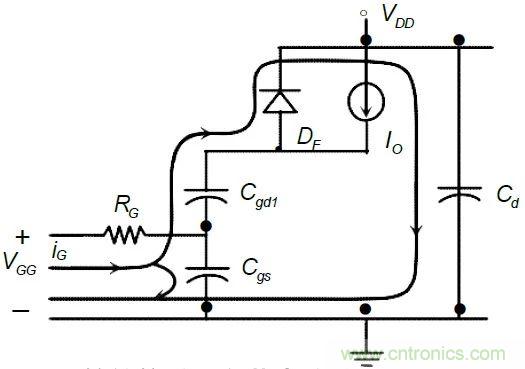

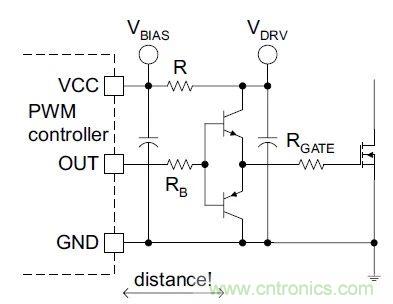

4.2 推挽式驱动

PWM 驱动通过推挽结构来驱动栅极

特点:实现较小的驱动环路和更大的驱动电流,栅极电压被钳位在 Vb+Vbe 和 GND 与Vbe 之间。

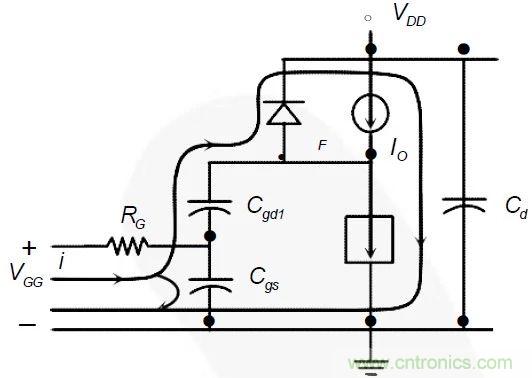

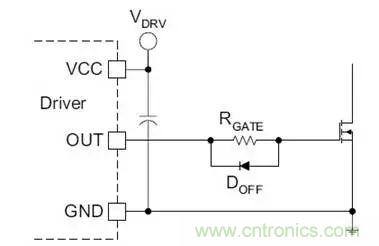

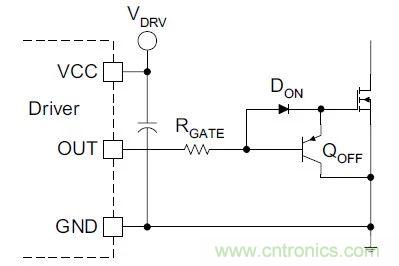

4.3 栅极驱动加速电路

并联二极管可以分流,但是随着电压降低,二极管逐渐失去作用。

4.4 PNP关断电路

特点:PNP 在关断时形成短路放电,但是无法完全为 0,二极管 Don 可以钳位防止三极管击穿。

五、 小结

以上大概详细介绍了MOS管这一半导体基础元器件的工作原理和应用,具体到工作中还需要的是实际测试和实验,特别是不断在一些应用中,尤其是应用问题中加深理解。这样或许才能真正的把相关基础知识融入到自己的能力中,游刃有余的解决技术问题。搞技术嘛,和做人一样,从小处做,往高处看。

原创: 硬汉

参考:

● Power MOSFET Avalanche Guideline----SungmoYoung, Application Engineer

● Analysis of dv/dt Induced Spurious Turn-onof MOSFET

● Prediction of MOS switching-off loss basedon parameters of datasheet

● Power MOS FET Application Note

● Design And Application Guide for HighSpeedMOSFET Gate Drive Circuits

推荐阅读:

深度解析:环路分析测试原理

通信工程师们都想要的超薄μModule解决方案来了

电机控制软件开发套件启动新设计

信号耦合对于回路面积控制的意义

噪声对策应遵循哪几个步骤?